|

|

|

Despre FPGA-uri și radioamatorismPartea I — Generalități

https://www.alauda.ro

De ceva timp mă pasionează FPGA-urile.

Sursele prezintă diverse soluții hardware și arhitecturi de procesare

bazate pe tehnologia FPGA, acoperind atât segmentul educațional,

cât și cel al comunicațiilor radio avansate.

Un document central detaliază specificațiile tehnice ale unui transmițător digital,

analizând setul de instrucțiuni al procesorului CPU16B și algoritmii de filtrare a semnalului.

În paralel, este explorat proiectul open-source Hermes Lite 2,

un transceiver pentru radioamatori ce utilizează cipuri modem de bandă largă

pentru procesarea directă a semnalelor HF. Articolele includ, de asemenea,

recomandări de plăci de dezvoltare Digilent, precum Nexys sau Basys,

adaptate pentru diferite niveluri de expertiză. În ansamblu, textele oferă

o perspectivă tehnică asupra modului în care logica programabilă facilitează

prototiparea rapidă și implementarea sistemelor de radio definit prin software.

Un FPGA (Field-Programmable Gate Array) este un circuit integrat programabil

pe care îl poți configura pentru a deveni aproape orice tip de circuit digital dorești.

Spre deosebire de un procesor obișnuit (CPU) care execută instrucțiuni una după alta,

un FPGA îți permite să construiești hardware-ul propriu-zis care să execute sarcini în paralel

De ce este un FPGA special? Fiindcă se comportă ca un fel de hardware lichid

Conceptul de hardware lichid este un concept fascinant

deoarece permite stocarea configurației hardware într-o memorie și schimbarea completă a funcției cipului

în câteva secunde doar prin reconfigurarea cu un alt fișier-cod software.

Aceeași placă FPGA poate fi azi un receptor radio, mâine un controler

de robot și poimâine un accelerator pentru inteligență artificială

Limbajele de programare care permit acest lucru sunt grupate sub

denumirea generică de hardware description languages — HDL.

Fișierul de configurare utilizat pentru programarea FPGA este numit bitstream.

Aceasta transformă radical modul în care sunt proiectate și utilizate sistemele electronice,

oferind câteva avantaje fundamentale:

În esență, „hardware-ul lichid” îmbină flexibilitatea software-ului cu

performanța hardware-ului dedicat, permițând crearea unor dispozitive care

arată ca un circuit integrat personalizat, dar care pot fi reprogramate oricând pentru noi sarcini.

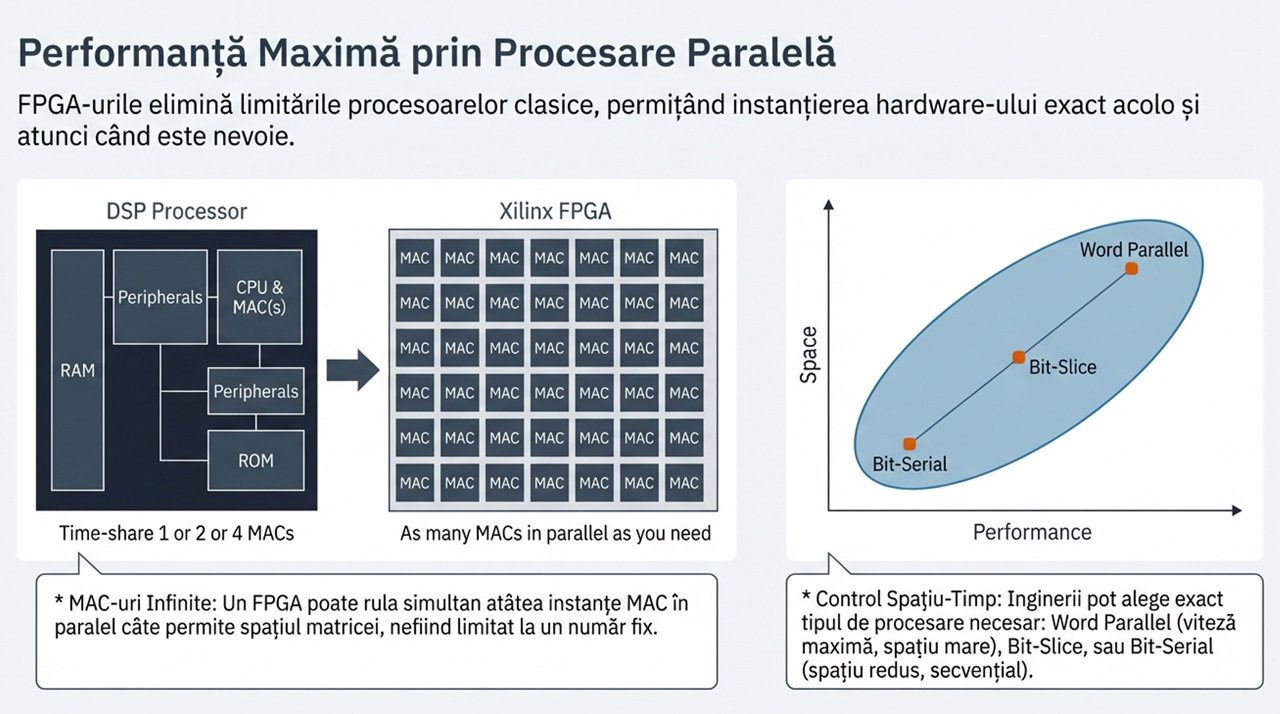

Paralelism, paralelism, paralelism — Avantajul major este paralelismul.

În timp ce un microprocesor are doar câteva unități de calcul care fac lucrurile pe rând,

un FPGA poate avea mii de unități denumire MAC (Multiply-Accumulate).

Acestea lucrează simultan. De exemplu, în procesarea semnalelor radio,

un FPGA poate efectua miliarde de operații pe secundă, depășind de multe ori

performanța unui procesor clasic. Pentru cei interesați de o analiză comparativă DSP vs FPGA,

un articol mai complex pe această temă poate fi accesat pe site-ul meu.

Pentru acest articol este suficient de spus că procesarea parelelă este mult mai ușor de implementat

pe un FPGA decât pe un DSP și implică mult mai puține riscuri de a greși în programare.

Programatorii de C++ se împart în programatori mediocri, excepționali și programatori de

multithreading (o specie aparte). Eu fac parte din prima categorie.

Imaginează-ți o tablă imensă de piese LEGO care pot fi reconectate prin software.

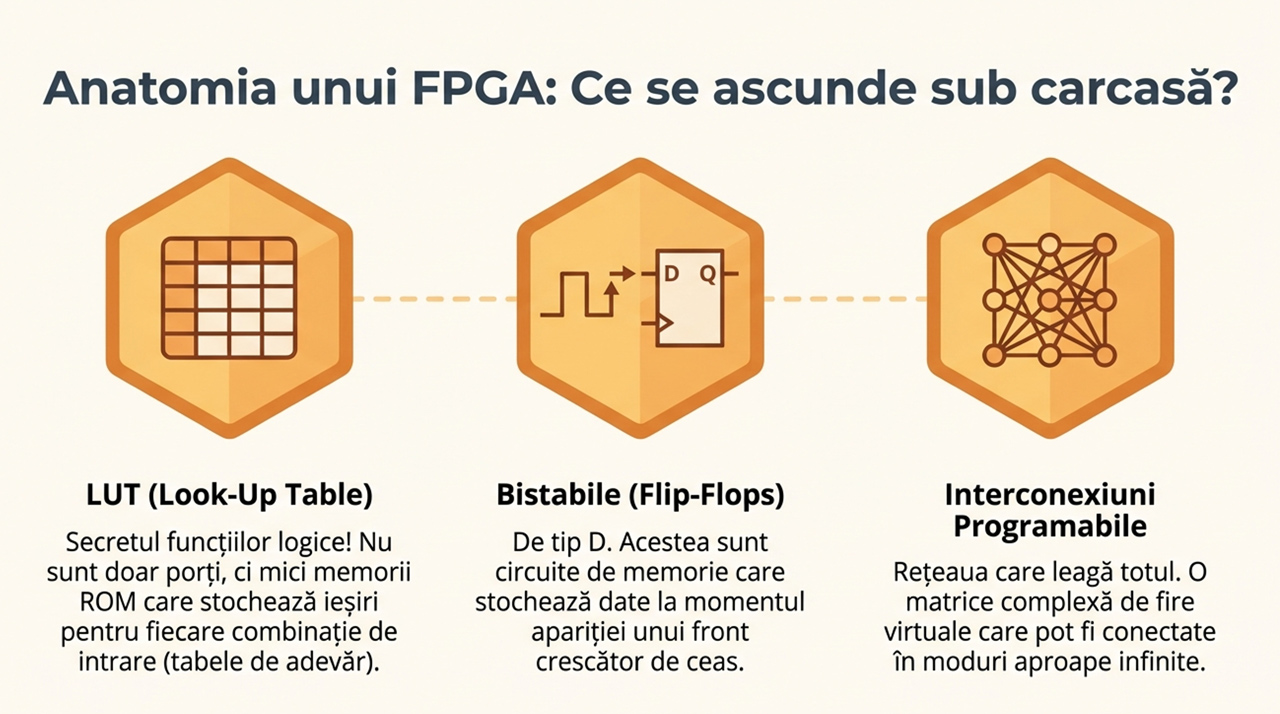

Arhitectura sa internă se bazează pe trei elemente principale:

Funcționarea LUT-urilor (Look-Up Tables) ca un tabel de adevăr

reprezintă secretul din spatele implementării logicii programabile

pe plăcile FPGA. În loc să utilizeze porți logice interconectate fizic

într-un mod fix, FPGA-ul folosește memorii pentru a simula comportamentul circuitelor digitale.

Iată mecanismul prin care LUT-urile îndeplinesc acest rol:

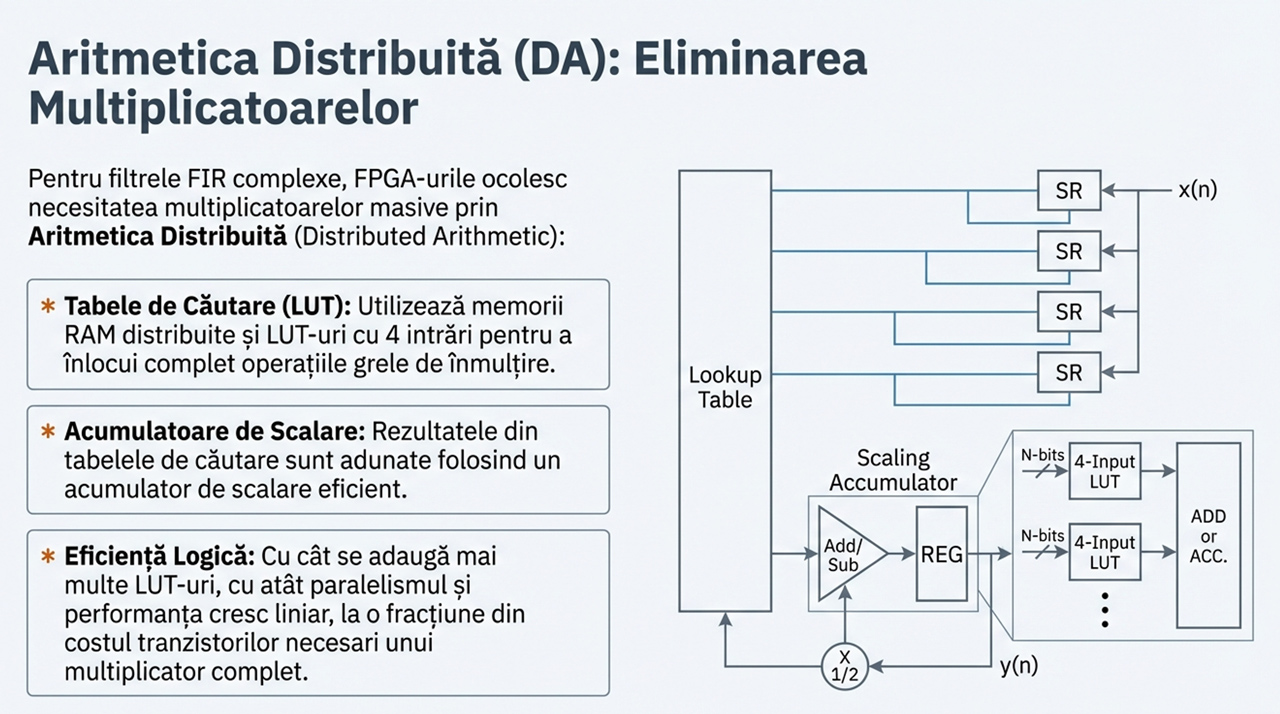

Aritmetică distribuită — Un exemplu de Filtru cu impuls finit (FIT).

Fiecare LUT este conectat la mai mulți regiștri de salt (shift registers - SR)

evitând necesitatea multiplicatoarelor. Prin acest sistem, LUT-urile permit FPGA-ului să execute funcții

logice complexe într-un mod extrem de flexibil, fiind elementul de bază

al blocurilor programabile care formează matricea cipului.

Nu programezi un FPGA în sensul tradițional (ca pe un PC),

ci îi descrii structura hardware folosind, cum spuneam, limbaje de descriere hardware

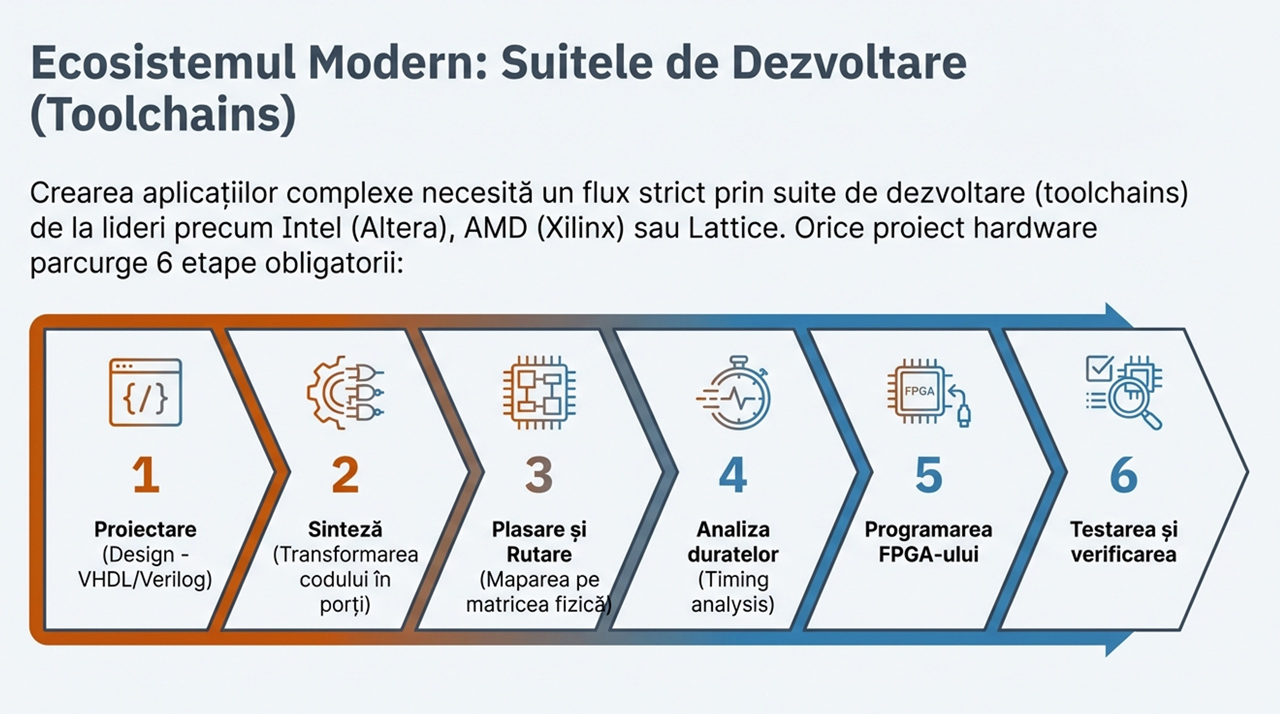

precum Verilog sau VHDL. Procesul prin care ideea ta ajunge pe cip include:

Hai să vedem un pic mai în detaliu ce se petrece în fiecare etapă. Ne vom concentra doar pe cele mai importante.

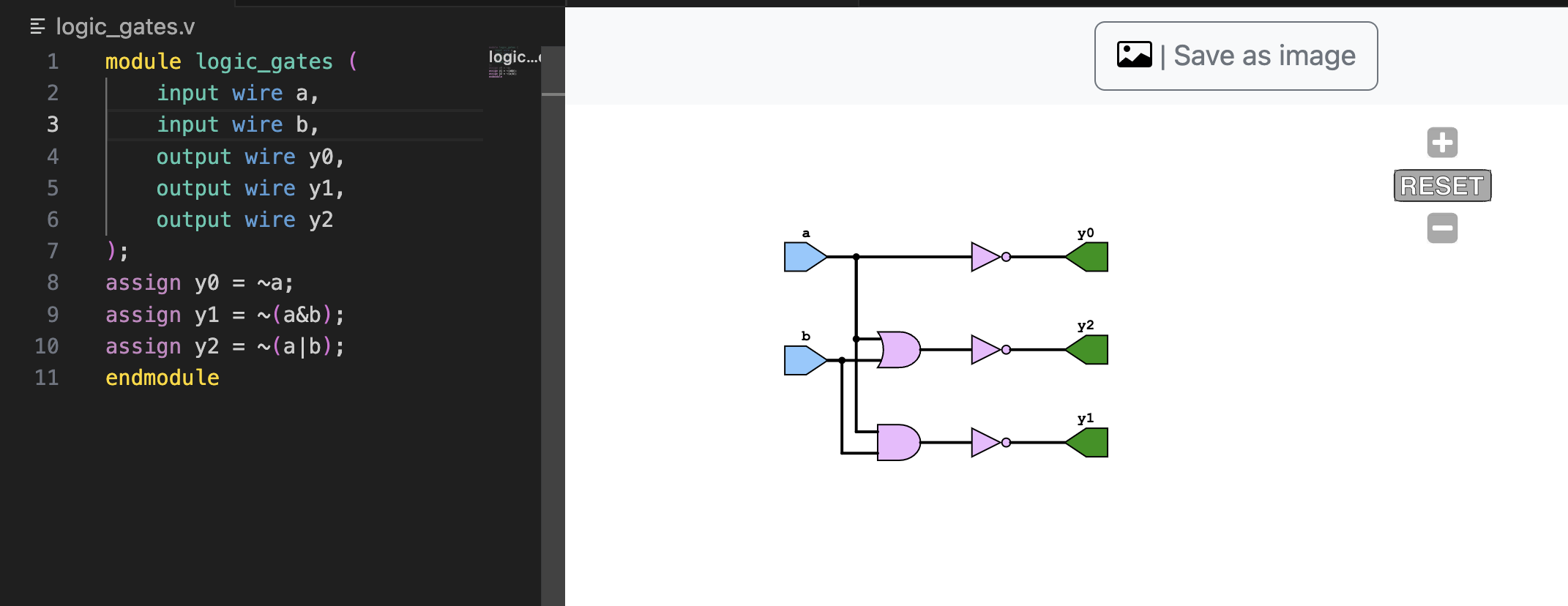

Elaborarea este primul pas prin care ideile tale scrise sub formă de cod

(cum este Verilog, SystemVerilog sau VHDL) încep să prindă viață ca circuit.

Iată ce se întâmplă, mai exact, în această etapă:

În esență, elaborarea creează un „desen” generic al circuitului tău,

pregătindu-l pentru etapa de sinteză, unde acest desen va fi adaptat exact

la „piesele” disponibile pe cipul tău specific

Elaborarea — procesul de elaborare așa cum apare el pentru

un proiect extrem de simplu de trei porți logice (NON, NAND și NOR).

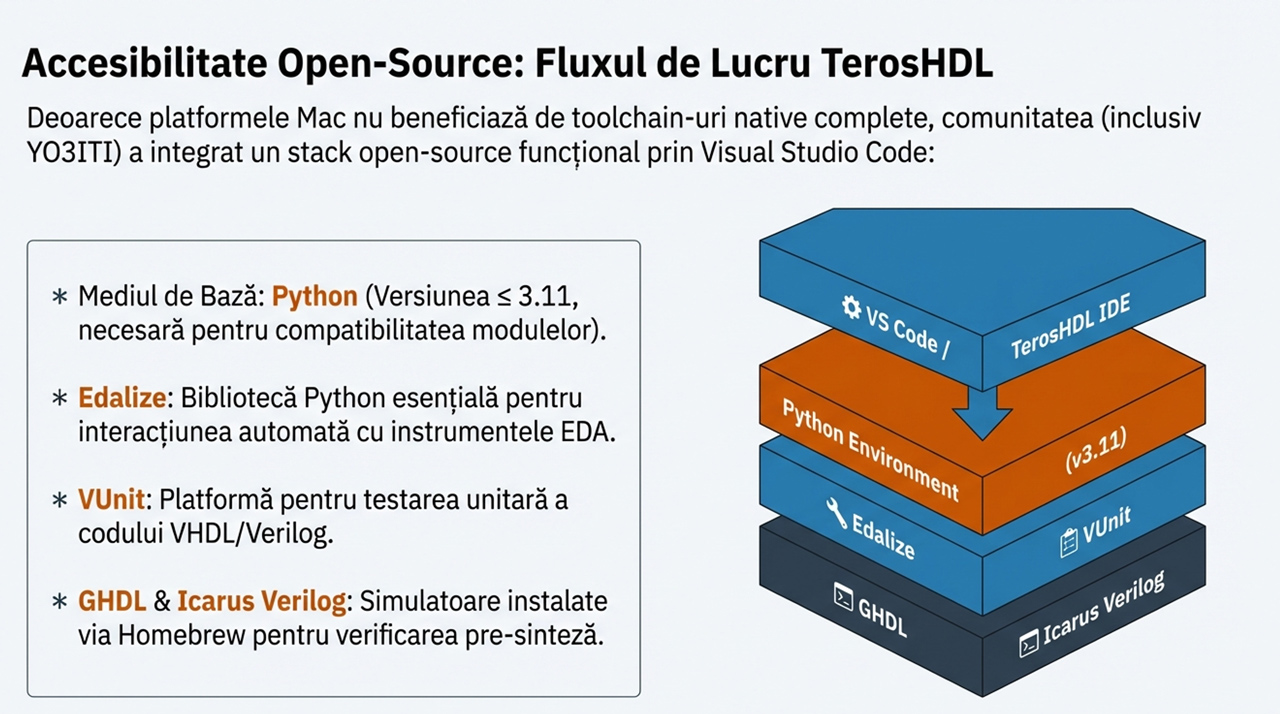

Toolchain: Visual Studio Code cu Modulul

TerosHDL

și Edalize,

VUnit,

GHDL

și Icarus Verilog pe Mac OS.

În stânga imaginii se observă codul HDL scris în Verilog. În dreapta, schema circuitului

rezultată în urma procesului de elaborare. Principalii vendori de FPGA (Intel/Altera,

AMD/Xilinx, Lattice, Microchip) nu furnizează platforme de dezvoltare pentru Mac OS.

Folosesc acest toolchain pentru prototipare rapidă și testare deoarece TerosHDL oferă doar

procesul de elaborare.

Procesul de sinteză este etapa în care ideile tale scrise sub formă de cod

(cum ar fi Verilog sau VHDL) încep să prindă o formă hardware specifică.

Dacă etapa anterioară (elaborarea) doar desena o schemă logică generală,

sinteza face următoarele lucruri esențiale:

În esență, sinteza este procesul de „traducere” a limbajului tău de programare

în instrucțiuni pe care componentele fizice ale FPGA-ului (LUT-uri, registre, multiplexoare)

le pot înțelege și executa.

După ce sinteza s-a terminat cu succes, urmează procesul de

Implementare/ Plasare și rutare (Place and Route), unde aceste „tabele” sunt așezate fizic pe cip.

Procesul de Place and Route (Plasare și Rutare) reprezintă

inima etapei de implementare a unui proiect FPGA.

Acesta are loc după ce codul tău (scris de obicei în Verilog sau VHDL)

a fost deja transformat în elemente logice generice prin etapa de sinteză.

Iată explicația acestui proces, împărțită în cele două componente ale sale:

De ce este acest proces special? Spre deosebire de un procesor

unde circuitele sunt fixe, în FPGA procesul de Place and Route

este cel care definește fizic circuitul tău. Rezultatul acestui proces

este transformat într-un fișier final de configurare numit bitstream.

Când descarci acest bitstream în memoria FPGA-ului,

el activează exact acele conexiuni și configurează blocurile logice

(LUT-urile) stabilite în timpul plasării și rutării,

transformând cipul într-o soluție hardware personalizată pentru aplicația ta.

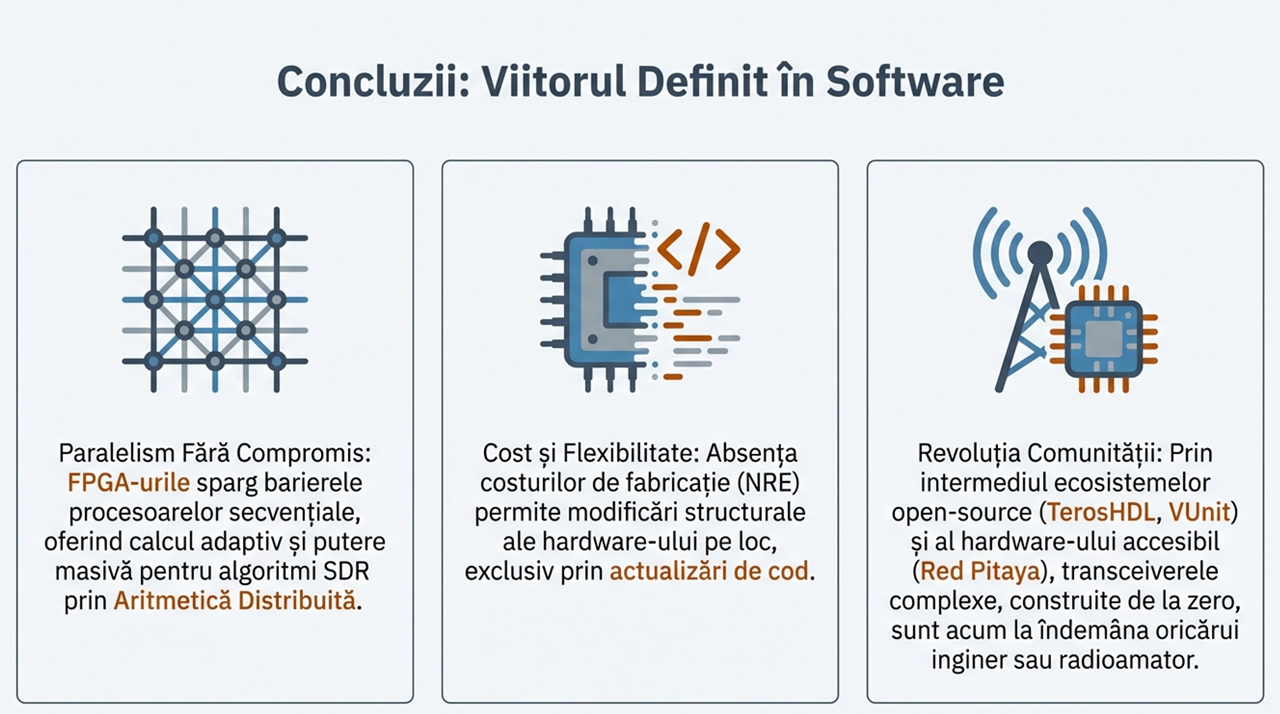

În concluzie, să adunăm ideile principale și să aruncăm o privire spre ce ne rezervă viitorul. Viitorul pare să fie reconfigurabil.

Dacă ar fi să reținem trei lucruri din această scurtă și foarte sumară introducere... care ar fi superputerea FPGA-urilor, acestea ar fi

În seriile următoare vom trece, pas cu pas, la aspecte din ce în ce mai apropiate

de implementarea practică în diverse proiecte radioamatoricești. Stay tuned. ;) 73

Articol aparut la 2-3-2026 73 Inapoi la inceputul articolului | |

La acest articol nu se (mai) primesc comentarii.

Opiniile exprimate în articole pe acest site aparţin autorilor şi nu reflectă neapărat punctul de vedere al redacţiei.

Copyright © Radioamator.ro. Toate drepturile rezervate. All rights reserved

Articole | Concursuri | Mica Publicitate | Forum YO | Pagini YO | Call Book | Diverse | Regulamentul portalului | Contact